Troubleshooting Sequential Logic Circuits

1. Tujuan1. mengetahui mengenai sequential logic circuits

2. Mampu membuat rangkaian sequential logic

[kembali]

2. Komponen

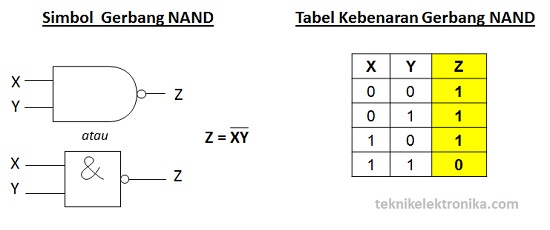

- Gerbang NAND

Arti NAND adalah NOT AND atau BUKAN AND, Gerbang NAND merupakan kombinasi dari Gerbang AND dan Gerbang NOT yang menghasilkan kebalikan dari Keluaran (Output) Gerbang AND. Gerbang NAND akan menghasilkan Keluaran Logika 0 apabila semua Masukan (Input) pada Logika 1 dan jika terdapat sebuah Input yang bernilai Logika 0 maka akan menghasilkan Keluaran (Output) Logika 1.

- Logicstate

-Logicprobe

[kembali]

3. Dasar Teori

Karena

gerbang logika standar adalah blok pembangun sirkuit kombinasional,

kait bistable dan sandal jepit adalah blok pembangun dasar dari

rangkaian logika sekuensial. Sirkuit logika sekuensial dapat dibangun

untuk menghasilkan flip-flop sederhana yang dipicu tepi atau sirkuit

sekuensial yang lebih kompleks seperti register penyimpanan, register

geser, perangkat memori, atau penghitung. Either way sirkuit logika

berurutan dapat dibagi menjadi tiga kategori utama berikut:

1. Event Driven - sirkuit asinkron yang segera berubah status saat diaktifkan

2. Clock Driven - sirkuit sinkron yang disinkronkan dengan sinyal jam tertentu

3. Pulse Driven - yang merupakan kombinasi dari keduanya yang merespons memicu pulsa.

Serta

dua keadaan logika yang disebutkan di atas tingkat logika "1" dan

tingkat logika "0", elemen ketiga diperkenalkan yang memisahkan sirkuit

logika berurutan dari rekan-rekan logika kombinasional mereka, yaitu

TIME. Sirkuit logika berurutan kembali ke kondisi semula semula begitu

reset dan sirkuit berurutan dengan loop atau jalur umpan balik dikatakan

bersifat "siklik".

Kita

sekarang tahu bahwa dalam rangkaian berurutan, perubahan hanya terjadi

pada penerapan sinyal clock yang membuatnya sinkron, jika tidak, sirkuit

tersebut tidak sinkron dan bergantung pada input eksternal. Untuk

mempertahankan keadaan mereka saat ini, sirkuit berurutan bergantung

pada umpan balik dan ini terjadi ketika sebagian kecil dari output

diumpankan kembali ke input dan ini ditunjukkan sebagai:

Sequential Feedback Loop

Dua inverter atau NOT gerbang dihubungkan secara seri dengan output di Q

diumpankan kembali ke input. Sayangnya, konfigurasi ini tidak pernah

berubah status karena output akan selalu sama, baik "1" atau "0", itu

diatur secara permanen. Namun, kita dapat melihat bagaimana umpan balik

bekerja dengan memeriksa komponen logika sekuensial paling dasar, yang

disebut SR flip-flop.

[kembali]4. Cara Kerja

Pertimbangkan

rangkaian yang ditunjukkan di atas. Jika input R berada pada level

logika “0” (R = 0) dan input S berada pada level logika “1” (S = 1),

gerbang NAND Y memiliki setidaknya satu dari inputnya pada logika “0”

oleh karena itu, outputnya Q harus pada level logika "1" (prinsip NAND

Gate). Output Q juga diumpankan kembali ke input "A" dan kedua input ke

NAND gate X berada pada level logika "1", dan oleh karena itu output

Q-nya harus pada level logika "0".

Lagi-lagi

kepala gerbang NAND. Jika reset input R berubah status, dan pergi

TINGGI ke logika "1" dengan S yang tersisa TINGGI juga pada level logika

"1", input gerbang NAND Y sekarang R = "1" dan B = "0". Karena salah

satu inputnya masih pada level logika "0" output pada Q masih tetap

TINGGI pada level logika "1" dan tidak ada perubahan status. Oleh karena

itu, rangkaian flip-flop dikatakan "Latched" atau "Set" dengan Q = "1"

dan Q = "0".

[kembali]

5. Bentuk Rangkaian

6. Video

[kembali]

7. Link Download

video download

HTML download

Data Sheet download

[kembali]

Tidak ada komentar:

Posting Komentar